SEPT 13

Issue 19/2007

www.edn.com

Signal Integrity:

Guest columnist

Gary Giust tackles

jitter peaking and PLLs

Pa 24

**EDN.comment**: PCB prototypes add value in the design process Pg 10

Design Ideas Pg 63

Supply Chain Pg 72

## Lower Power, Higher Performance

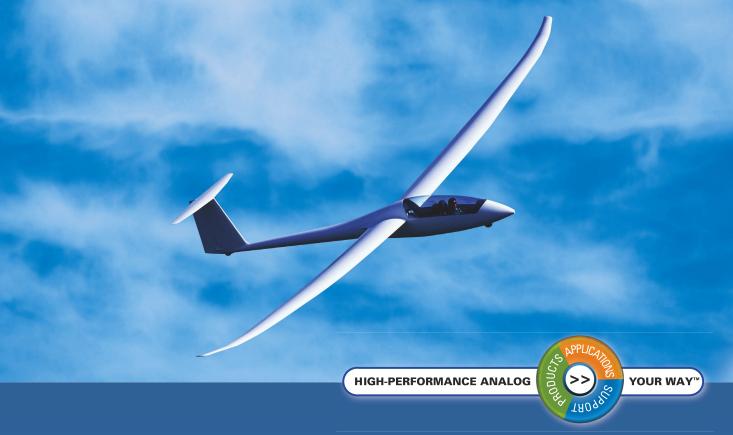

1μA, 1.8V, Zero-Crossover Op Amp

The **OPA369** precision amplifier from Texas Instruments is the industry's lowest power zero-crossover op amp. Featuring a unique single input stage architecture, the device achieves rail-to-rail performance without input crossover. With 1µA quiescent current, SC70 package and operation down to 1.8V, the OPA369 enables higher performance and simplifies designs in portable, battery-powered applications.

High-Performance Analog >> Your Way

For samples, datasheets and the new Amplifier and Data Converter Selection Guide, visit >> www.ti.com/opa369 800,477,8924 ext. 4023

High-Performance Analog >> Your Way, Technology for Innovators and the red/black banner are trademarks of Texas Instruments. 1885A0 © 2007 Ti

# AS OUTSICE THE DOX SCHOOLOGIES US INC. • AVEN AVX CORPORATION • B B BATTERY SHA OUTSICE THE DOX SCHOOLOGIES US INC. • BOURNS INC. • BRAND 77 TOOLS • BUD RIDUSTRI COMPONENTS/ITT INDUSTRIES • C-MAX • C-TON INDUSTRIES • CADDOCK • CANTHERM • CAPITAL ADVANCE OF ECHNOLOGIE ART SCHOOLOGIES ART SCHOO

Access to more than a million products now available online!\*

Same-day shipment, next-day delivery on orders entered by 8:00 PM CST.

Quality Electronic Components, Superior Service

www.digikey.com

1.800.344.4539

NNOVATIUN Leadership above all...

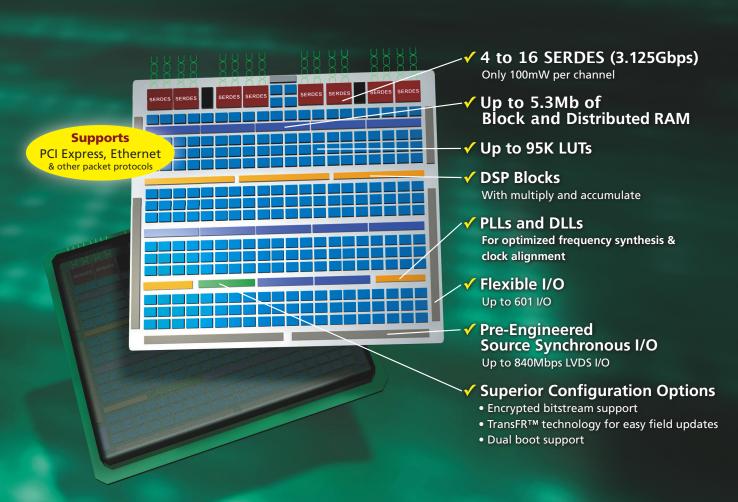

Xilinx brings your biggest ideas to reality:

Virtex™-5 FPGAs — Highest Performance. With multiple platforms optimized for logic, serial connectivity, DSP, and embedded processing, Virtex-5 FPGAs lead the industry in performance and density.

**Spartan**™-3 **Generation FPGAs** — **Lowest Cost.** A unique balance of features and price for high-volume applications. Multiple platforms allow you to choose the lowest cost device to fit your specific needs.

**CoolRunner**<sup>™</sup>-**II CPLDs** — **Lowest Power.** Unbeatable for low-power and handheld applications, CoolRunner-II CPLDs deliver more for the money than any other competitive device.

ISE™ Software — Ease-of-Design. With SmartCompile™ technology, users can achieve up to 6X faster runtimes, while preserving timing and implementation. Highest performance in the fastest time — the #1 choice of designers worldwide.

Visit our website today, and find out why Xilinx products are world renowned for leadership ... above all.

At the Heart of Innovation

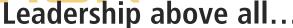

## **CAN Transceivers**

**Versatile, Low-Power, 3-V and 5-V Solutions**

#### **Applications**

- Industrial automation

- Low-power battery applications

- DeviceNet, CANopen, Safety BUS

- SAE J1939 truck, bus, construction interface

- NMEA 2000 and SeaTalk2 Marine interface

- ISOBUS ISO11783 agricultural interface

#### **Features**

- Industry-leading ESD on bus pins delivers reliability in harsh environments

- 5μA standby mode w/remote wake-up for battery applications or nodes that can be powered down

- Autobaud loopback function allows glitch-free insertion into a live bus with an unknown baud rate

HIGH-PERFORMANCE ANALOG

Texas Instruments has a portfolio of CAN transceivers that will meet your standards and exceed your expectations regardless of your design concerns – ESD, power consumption, EMI immunity or bus leakage. Our 3-V and 5-V transceivers are drop-in upgrades for new or existing designs with capabilities like autobaud loopback, sleep-mode standby and bus monitoring w/remote wake-up.

| Device      | I/O and<br>V <sub>CC</sub><br>Levels (V) | Short-Circuit<br>Protection<br>(V) | ESD<br>(kV) | Supply<br>Current<br>(mA) | Stand-By<br>Current<br>(µA) | Features                                                 |

|-------------|------------------------------------------|------------------------------------|-------------|---------------------------|-----------------------------|----------------------------------------------------------|

| SN65HVD230  | 3                                        | -4 to +16                          | 16          | 17                        | 370                         | Low-Power Standby                                        |

| SN65HVD231  | 3                                        | -4 to +16                          | 16          | 17                        | 0.04 Sleep                  | Ultra-Low-Power Sleep                                    |

| SN65HVD232  | 3                                        | -4 to +16                          | 16          | 17                        | NA                          | Economical                                               |

| SN65HVD233  | 3                                        | -36 to +36                         | 16          | 6                         | 200                         | Standby, Diagnostic Loopback                             |

| SN65HVD234  | 3                                        | -36 to +36                         | 16          | 6                         | 200/0.05 Sleep              | Standby, Ultra-Low-Power Sleep                           |

| SN65HVD235  | 3                                        | -36 to +36                         | 16          | 6                         | 200                         | Autobaud Loopback; Standby                               |

| SN65HVD251  | 5                                        | -36 to +36                         | 14          | 14                        | <275                        | Low-Power Standby                                        |

| SN65HVD1040 | 5                                        | -27 to +40                         | 12          | 10                        | 5                           | Low-Power Standby with Bus<br>Wake-Up, Dominant Time-Out |

| SN65HVD1050 | 5                                        | -27 to +40                         | 8           | 6                         | NA                          | Listen-Only Mode, Dominant Time-Out                      |

Parts shown in red are newly released

High-Performance Analog >> Your Way, Technology for Innovators and the red/black banner are trademarks of Texas Instruments. 1900A0 © 2007 TI

For samples, simulation models and reference design demo, visit >> www.ti.com/cantransceivers 800.477.8924, ext 14006

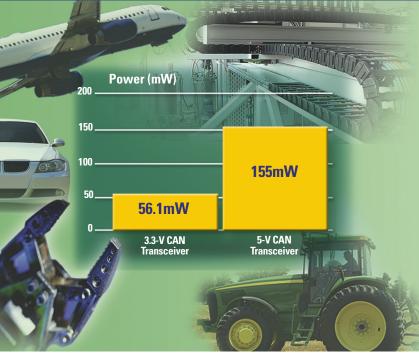

## **RGB LED Driver Generates Highly Efficient** "True White" Backlighting

LP5520 Provides Innovative, Easy-to-Use, Instant Color Gamut Improvement for **Small Format Displays**

#### **Key Features**

- Temperature compensated LED intensity and color 100% NTSC color gamut, brighter color, better picture quality

- Individual calibration coefficients for each color

- Color accuracy  $\Delta X$  and  $\Delta Y \leq 0.003$

- User programmability for effects, aging, dimming

- PWM control inputs for each color

|     | Product | Description                                                                                                                                      | Packaging           |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| NEW | LP5520  | RGB Backlighting LED driver with integrated white balance compensation                                                                           | microSMD-25         |

| NEW | LP5521  | Programmable, low power, 3-channel LED driver                                                                                                    | microSMD-20, LLP-24 |

| NEW | LP5522  | Autonomous single LED controller with one wire interface                                                                                         | microSMD-6          |

|     | LP5526  | Lighting Management Unit with high voltage boost converter with up to 150 mA serial flash LED driver                                             | microSMD-25         |

|     | LP5527  | LED driver for camera flash and 4 LEDs with $\ensuremath{\mbox{l}^2\mbox{C}}$ programmability, LED connectivity, test, and audio synchronization | microSMD-30         |

| NEW | LP55281 | 13 channel LED driver with audio sync, LED connectivity test and independent PWMS/PWMS blinking cycles                                           | microSMD-36         |

Ideal for navigation systems, mobile phones, medical devices, and other portable devices

For FREE samples, datasheets, and more information on the LP5520, contact us today at: led.national.com

Or call: 1-800-272-9959

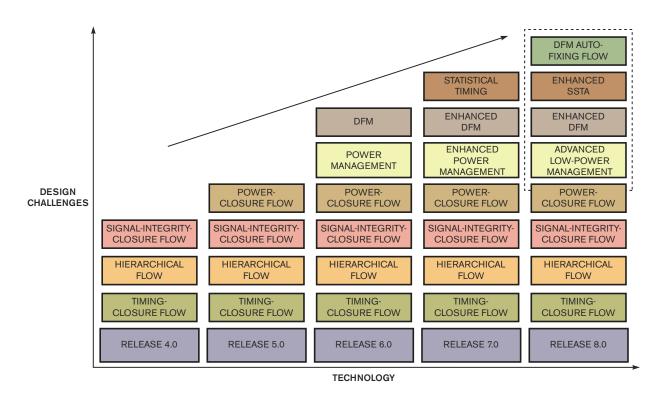

#### How low can you go? A look at 45-nm-ICdesign challenges

If you have tools for the 65-nm or even the 90-nm node, moving to the 45-nm node requires no retooling. But designers moving to this node must adopt some advanced design techniques and be aware of some new design rules that foundries have imposed to ensure that SOC designs yield acceptable results.

by Michael Santarini, Senior Editor

#### Permanent-magnet motors boost efficiency and power density

Sensorless versions of these highly efficient motors reduce cost and parts count, but the motors still require complex control algorithms. Match the right motor type and controller to your application for the best performance and cost.

> by Margery Conner, Technical Editor

## EDN contents

9.13.07

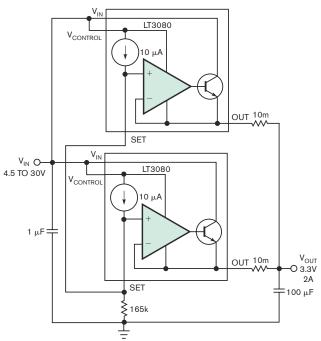

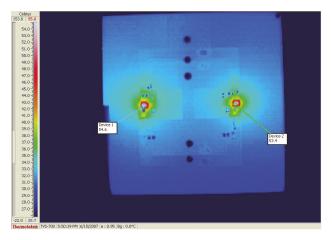

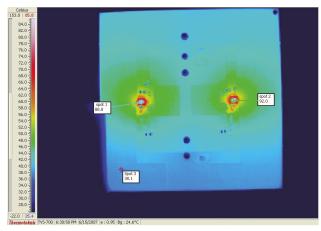

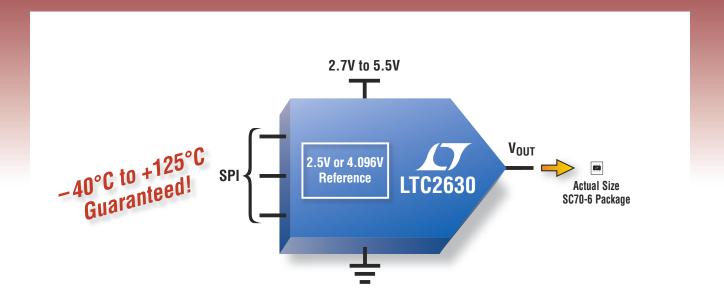

#### Distributed linear regulators increase output current and spread the heat

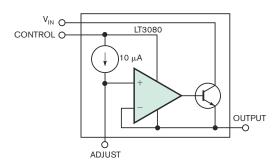

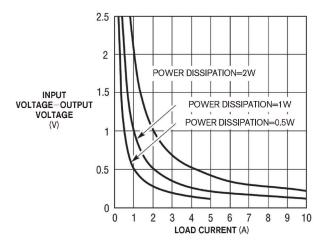

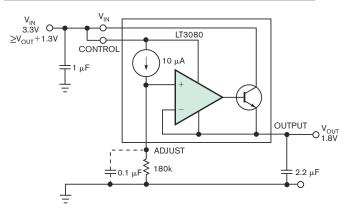

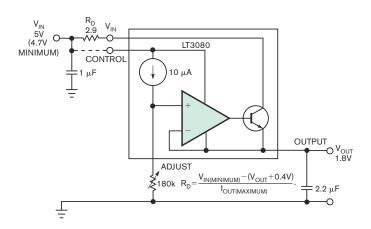

Parallel-board layout and heat spreading provide designers new ways to use linear regulators in all-surface-mount approaches. These techniques work well in today's high-performance, high-density PCBs.

> by Robert Dobkin, Linear Technology Corp

## GNIDEAS

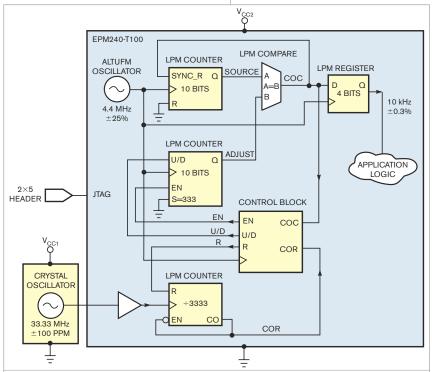

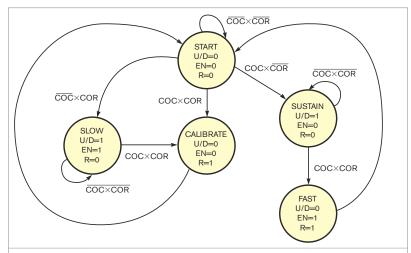

- 63 CPLD's internal oscillator performs autocalibration

- 64 Swapping bits improves performance of FPGA-PWM counter

- 66 Relays eliminate high-voltage noise

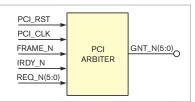

- 70 VHDL program enables PCI-bus-arbiter core

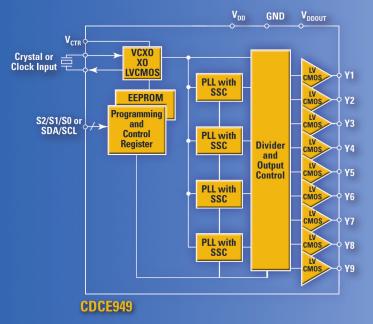

## Flexible Clock Generators

### Multiple I/O-V and Programmability Ease System Design

#### **Applications**

- Digital media systems (audio/video)

- IP-STB/TV/phone

- Streaming media (DVD-P/R)

- GPS receivers

- Portable media and printers

- TI DSP, OMAP™ and DaVinci™ media processors

#### **Features**

- 1.8V, 2.5V and 3.3V I/O

- 1 to 4 PLLs

- Spread Spectrum Clocking (SSC) reduces affects of EMI

- I<sup>2</sup>C and EEPROM programmability

- On-chip Voltage Controlled Crystal Oscillator (VCXO)

- 14-, 16-, 20- and 24-pin TSSOP

HIGH-PERFORMANCE ANALOG

Texas Instruments produces a portfolio of low-power, low-jitter, programmable clock generators capable of generating up to nine output clocks from a single input frequency – each output is programmable in-system for any clock frequency up to 230MHz. This level of functionality provides the system designer with capabilities previously unavailable in clock/timing products.

| Device   | Supply Voltage (V) | I/O Voltage (V) | # of PLL | # of Outputs | Output Frequency (MHz) | Temperature Range (°C) | Package (TSSOP) |

|----------|--------------------|-----------------|----------|--------------|------------------------|------------------------|-----------------|

| CDCE949  | 1.8                | 2.5/3.3         | 4        | 9            | 230                    | -40 to +85             | 24              |

| CDCE937  | 1.8                | 2.5/3.3         | 3        | 7            | 230                    | -40 to +85             | 20              |

| CDCE925  | 1.8                | 2.5/3.3         | 2        | 5            | 230                    | -40 to +85             | 16              |

| CDCE913  | 1.8                | 2.5/3.3         | 1        | 3            | 230                    | -40 to +85             | 14              |

| CDCEL949 | 1.8                | 1.8             | 4        | 9            | 230                    | -40 to +85             | 24              |

| CDCEL937 | 1.8                | 1.8             | 3        | 7            | 230                    | -40 to +85             | 20              |

| CDCEL925 | 1.8                | 1.8             | 2        | 5            | 230                    | -40 to +85             | 16              |

| CDCEL913 | 1.8                | 1.8             | 1        | 3            | 230                    | -40 to +85             | 14              |

Part shown in red is newly released

For samples, evaluation modules, visit>> www.ti.com/programmableclocks 800.477.8924, ext. 13971

OMAP, DaVinci, High-Performance Analog >> Your Way, Technology for Innovators and the red/black banner are trademarks of Texas Instruments. 1901A0 © 2007 TI

#### contents 9,13.07

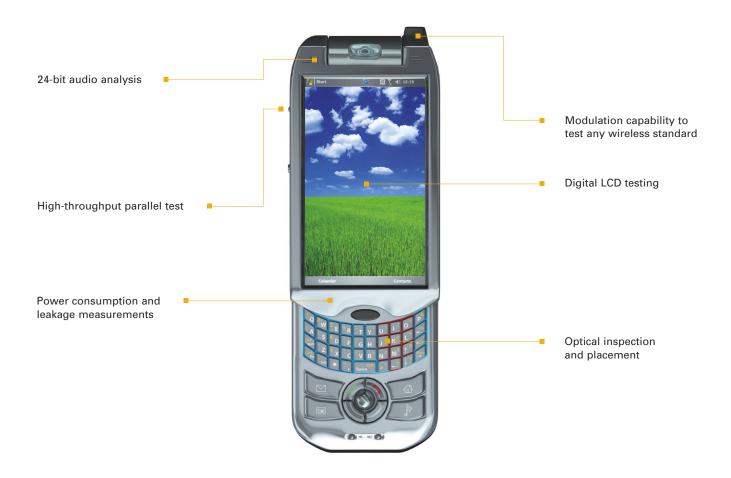

- USB-powered RF-power sensor combines most measurement functions

- 16 Video-codec cores offer programmability

- 18 Cadence and Mentor create free, open-source SystemVerilog methodology

- 20 Processor lowers the cost and power thresholds for HD video

- 20 Reference design prevents power theft

- Module controls four network channels

- Research Update: Los Alamos lab makes major step in quantum-dot lasers; Silicon nanocrystals promise 40% solar-cell efficiency; Nanostructures enable paperlike supercapacitors and batteries

#### **DEPARTMENTS** & COLUMNS

- 10 EDN.comment: PCB prototypes add value in the design process

- Signal Integrity: Jitter peaking and PLLs

- 72 **Supply Chain:** Start-up customers: diamonds in the rough; Outsourcing by OEMs pushes EMS, ODM growth; Norway POHS casts wide net

- 76 Scope: The AES Convention, a 1950s microcontroller, and SOC architectures

#### **PRODUCT** ROUNDUP

74 Sensors and Transducers: LVDT-position transmitters, analog accelerometers with MEMS sensors and CMOS-interface chips, and an RTD temperature-sensor family

EDN® (ISSN#0012-7515), (GST#123397457) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer. Periodicals postage paid at Littleton, CO 80126 and additional mailing offices. Circulation records are maintained at Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN® copyright 2007 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$165 one year, Canada, \$226 one year, (includes 7% GST, GST#123397457); Mexico, \$215 one year, air expedited, \$398 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Agreement No. 40685520. Return undeliverable Canadian addresses to: RCS International, Box 697 STN A, Windsor Ontario N9A 6N4. E-mail: Subsmail@ReedBusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevie Properties Inc, used under license. A Reed Business Information Publication/Volume 52, Number 19 (Printed in USA).

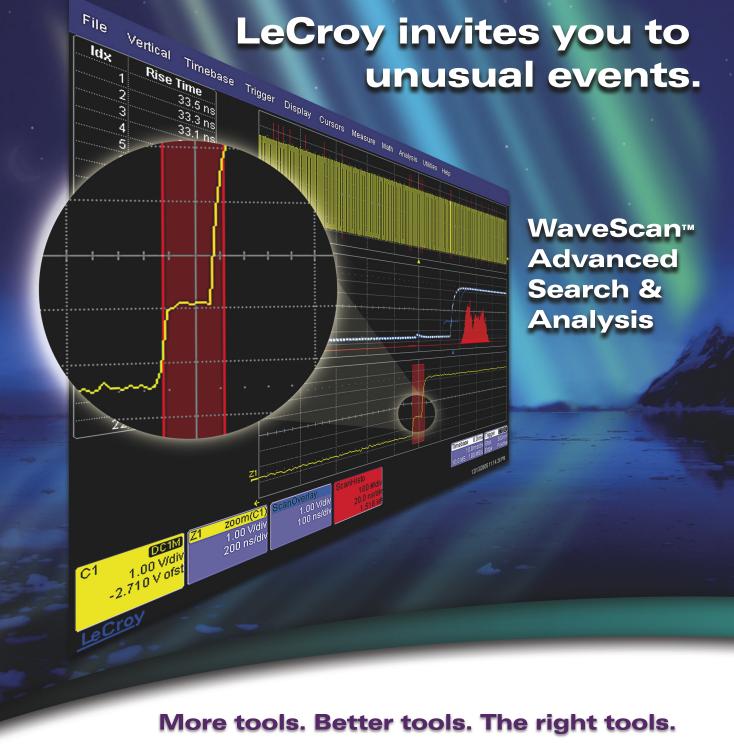

WaveScan, a powerful new tool only for LeCroy oscilloscopes, continuously monitors live acquisitions for unusual events – even if you're not there.

Select from more than 20 search criteria, including frequency, rise time, runt, and duty cycle. WaveScan also locates rare occurrences in a single capture, or even a saved waveform and marks events for quick identification. Debug faster. It's that simple.

EDN Magazine has included LeCroy's WaveRunner® Xi and WaveSurfer® Xs with WaveScan in it's 'Hot 100 Products' list. WaveScan is also an EDN 2007 Innovation Award Finalist.

## online contents

**BUSINESS CENTERS**

www.edn.com

MORE...

**NEWS CENTER**

#### ONLINE

Check out these Web-exclusive articles:

#### Hybrid cabling combines low-cost, versatility

Hybrid cabling uses the principal advantages of point-to-point wiring and systems cabling, while minimizing the weaknesses of each

→www.edn.com/article/CA6469197

#### Designing an efficient power inductor for mobile-computing applications

→www.edn.com/article/CA6468654

#### End-user realities impact chip architecture in the video-surveillance market

→www.edn.com/070913toc1

#### WiiConnect: Make sure your wireless channel's correct

→www.edn.com/070913toc2

#### United States versus Asia: Education, Gordon Moore, and Star Trek

→www.edn.com/070913toc3

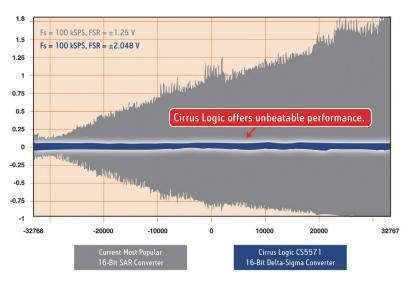

#### Kenet 12- and 14-bit ADCs: Specs show real breakthroughs

→www.edn.com/070913toc4

#### Pow! Crack! Kablam! Clash of the digicam image-sensor titans

→www.edn.com/070913toc5

#### China is not the problem (Companies that outsource are)

→www.edn.com/070913toc6

#### Smart, small fan controllers and temperature monitors support PCs, embedded systems

→www.edn.com/article/CA6471149

**DESIGN CENTERS**

#### READERS' CHOICE

A selection of recent articles receiving high traffic on www.edn.com.

#### Prying Eyes: Inside Apple's iPhone

See which ICs Apple's engineers selected, and ponder the architecture decisions that hint at future iPhone generations.

→ www.edn.com/article/CA6463808

#### Researchers debut paperlike battery device

→www.edn.com/article/CA6468724

#### Applying solenoids:

#### Flying blind is not recommended

→ www.edn.com/article/CA6462567

#### 64-core processor tip of the multicore iceberg for start-up Tilera

→www.edn.com/article/CA6470108

#### Home transportation: benchmarking power line, 802.11, and Ethernet

→ www.edn.com/article/CA6462560

#### Can anyone get chip design right the first time?

→www.edn.com/article/CA6467367

#### A digital picture frame is worth 1000 words

→www.edn.com/article/CA6462566

#### Plextronics claims organic-solar-cell efficiency record

→www.edn.com/article/CA6467197

#### Hynix licenses Innovative Silicon SOI DRAM technology

→www.edn.com/article/CA6467841

#### Modified Prius gets more than 100 mpg with lithium-ion batteries

→www.edn.com/070913toc10

PART SEARCH

#### FROM EDN's BLOGS

#### Near-invisible user interface improvements

From Embedded Processina. by Robert Cravotta

For the increasing number of end products that supports software updates, the need to continue to improve the inner and invisible workings of a user interface can spell the difference between sustainable success and losing out to a competitor.

→www.edn.com/070913toc12

#### A FEAST OF FEEDS

EDN offers a range of RSS feeds. Whether you choose to subscribe to the "everything" feed, a feed for a specific design discipline, or a feed for a blog, you get the latest from EDN as soon as we publish it.

→www.edn.com/rss

#### **PART SEARCH**

EDN's Part Search, powered by SupplyFrame, provides the latest production prices, products specs, availability information, and leadtimes. Use this new tool for cross-referencing, getting instant quotes, and connecting quickly with authorized distributors.

#### BY MAURY WRIGHT, EDITORIAL DIRECTOR

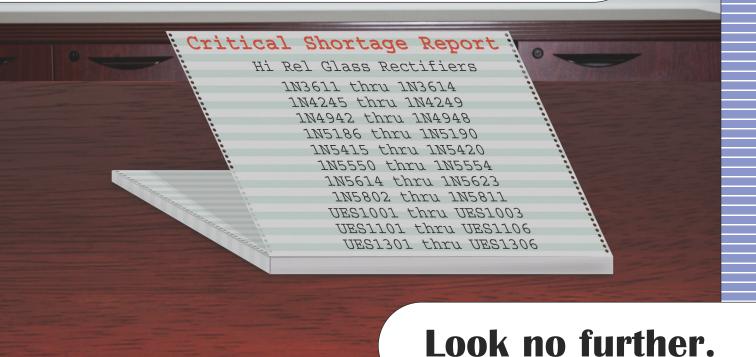

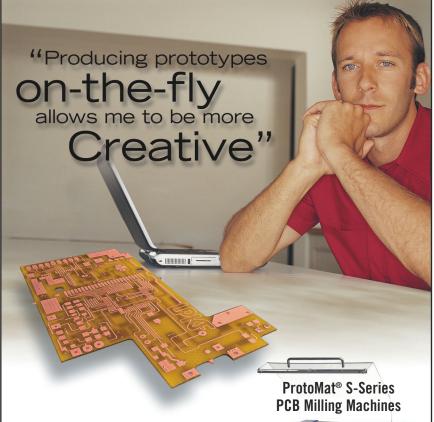

## PCB prototypes add value in the design process

spend a good portion of my time meeting with companies in the EOEM (electronics-original-equipment-manufacturing) market, and most of those meetings are with semiconductor vendors due to the vast number of such companies. But on a recent trip to the Northwest, I spent time with some different types of companies—two of which are involved in the prototype-PCB (printed-circuit-board) area. The meetings got me thinking about how engineers use prototype

PCBs in the design process. I'll offer up a few things I heard. I'm also hoping that you will respond in the Feedback Loop comment section located alongside the online version of this article and tell us and your fellow readers how you use prototype PCBs.

First, I met with LPKF Laser & Electronics (www.lpkfusa.com). LP-KF makes equipment that allows design engineers to quickly make their own prototype PCBs. A number of years ago, EDN ran a feature on this technology that you might find interesting: See www.edn.com/article/ CA45861. LPKF offers computer-controller PCB plotters along with milling machines and plating systems. For as little as \$10,000, you can buy the gear you need to build PCB prototypes, although the price can escalate based on your needs for multilayer and SMT (surface-mount-technology) support. The company even offers laser-based plotters for small pro-

LPKF President Stephan Schmidt claims that design engineers drive the purchase of most of the company's systems due to the need for building prototypes during the design process. Schmidt doesn't suggest that techI would have guessed that most designers ordering prototype PCBs would not order the PCB in the targetsystem form factor.

niques such as simulation aren't valuable. But he claims that designers often yield higher quality and better performing systems when they can do a series of prototypes to test the system architecture and design.

Even if you don't have an immediate need for a prototyping system in your lab, you might still want to request a copy of the LPKF catalog. In the back of the catalog, the company offers a technical guide on PCB manufacturing. Although the catalog presents the information relative to LPKF products, there is also good general information, including sections on design for microwave and RF systems and on SMT designs. LPKF is also worthy of praise for its efforts to encourage engineering education. The company pro-

vides refurbished gear to high-school pre-engineering programs.

Later in my trip, I met with Sunstone Circuits (www.sunstone.com), a manufacturer that specializes in prototype PCBs. Originally, Sunstone was in the production-PCB business, but almost all of the production-PCB business has moved to Asia. Sunstone allows designers to specify and order PCBs online and often can deliver products in two days. The company also offers free PCB-design software.

I would have guessed that most designers ordering prototype PCBs would not order the PCB in the target-system form factor. I'm accustomed to seeing reference designs and development boards with extra connections that offer access to interconnects between chips and to test ports. But Sunstone claims that 80 to 90% of its orders are in the target-system form factor. Rocky Catt, Sunstone's executive vice president and chief operating officer, claims that some designers will build prototype PCBs with more layers than the production board will use. For the prototype, the designer might rely on an autorouted layout that could lead to extra layers, whereas for the production board, the designer will hand-optimize the board to minimize the number of layers.

How do you use prototypes? Do you prototype only challenging parts of a system design? Do you iteratively build prototype PCBs to tune a design? How should *EDN* cover PCB design? Are we delivering information you need? You can certainly e-mail me or call me with answers, but by posting your comments online, your fellow readers can benefit from your thoughts as well.**EDN**

Contact me at mgwright@edn.com.

#### MORE AT EDN.COM

+ Go to www.edn.com/070913ed and click on Feedback Loop to post

a comment on this column.

## Maximize energy efficiency in every DC-DC design.

#### Here is a selection of our integrated DC-DC solutions:

| Product                                                                | Part Numbers*        | Features                                                                                                                                                             |

|------------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Integrated Switching<br>Regulators (Controller +<br>Drivers + MOSFETs) | FAN2106<br>FAN5350   | Up to 95% efficiency     Small, ultra-thin package (MLP and CSP)                                                                                                     |

| Power Controllers<br>(Controller + Drivers)                            | FAN6520              | Drives N-Channel MOSFETs in a synchronous buck topology     Output voltage range as low as 0.8V to V <sub>IN</sub>                                                   |

| Power Drivers (FET plus<br>Driver Multi-Chip Module)                   | FDMF8704<br>FDMF6700 | >85% efficiency     Optimal synchronous buck power stage DrMOS solutions     Unique MLP 6×6 package                                                                  |

| Integrated MOSFETs<br>(multiple MOSFETs<br>in one package)             | FDMS9600<br>FDMS9620 | 50% board space savings versus discrete solution     Ease of layout in PCB design     Optimized matching and sizing of MOSFETs (>92% efficiency)     MLP 5×6 package |

<sup>\*</sup>These products represent a small sampling of Fairchild's DC-DC portfolio.

No one offers more efficient DC-DC options than Fairchild. We combine perfectly matched power analog and discrete components with advanced packaging and power expertise for the industry's leading energy-saving portfolio. You can choose the optimum combination of controller, drivers and MOSFETs in a wide range of performance and size specifications.

Whatever your system performance and time-to-market needs may be, Fairchild has your ideal DC-DC solutions.

Learn more about all of our DC-DC solutions—including PWM controllers, voltage regulators and MOSFETs—at www.fairchildsemi.com/dcdc.

**Explore** design techniques and simulation technologies for IC, packaging, RF & microwave, system signal integrity, system-level EMI, low power and much more.

**Discover** how to design systems that integrate RF/Analog/Digital SoC solutions with memory, graphics, storage, antennas, displays, cameras, and MP3 players.

**Learn** how to integrate electromagnetic components, power electronic circuits, and controllers into high-performance electromechanical systems.

**Discuss** with industry leaders how to achieve first-pass system success!

Get more information and register online: ansoft.com/firstpass

#### PUBLISHER. EDN WORLDWIDE

Alan Robinson 1-408-345-4450; fax: 1-408-345-4400; aarobinson@reedbusiness.com

#### EDITORIAL DIRECTOR, EDN WORLDWIDE

Maury Wright, 1-858-748-6785; mawriaht@edn.com

#### EXECUTIVE EDITOR

Ron Wilson, 1-408-345-4427; ronald.wilson@reedbusiness.com

#### MANAGING FDITOR

Kasey Clark

1-781-734-8436; fax: 1-303-265-3053; kase@reedbusiness.com

#### EDITOR IN CHIEF, EDN.COM

Matthew Miller

1-781-734-8446; fax: 1-303-265-3017; mdmiller@reedbusiness.com

#### SENIOR ART DIRECTOR

Mike O'Leary 1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

#### EMBEDDED SYSTEMS

Warren Webb, Technical Editor 1-858-513-3713; fax: 1-858-486-3646; wwebb@edn.com

#### ANALOG

Paul Rako, Technical Editor 1-408-745-1994; paul.rako@reedbusiness.com

#### EDA, MEMORY, PROGRAMMABLE LOGIC

Michael Santarini, Senior Editor 1-408-345-4424: michael.santarini@reedbusiness.com

#### MICROPROCESSORS, DSPs. TOOLS

Robert Cravotta, Technical Editor 1-661-296-5096; fax: 1-303-265-3116; rcravotta@edn.com

#### MASS STORAGE, MULTIMEDIA, PCs AND PERIPHERALS

Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-303-265-3187; bdipert@edn.com

#### POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

#### DESIGN IDEAS EDITOR

Charles H Small edndesignideas@reedbusiness.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville, 1-781-734-8439; fax: 1-303-265-3131; f.granville@reedbusiness.com

#### ASSOCIATE EDITOR

Maura Hadro Butler, 1-617-276-6523; mbutler@reedbusiness.com

#### EDITORIAL/WEB PRODUCTION MANAGER

Diane Malone, Manager 1-781-734-8445; fax: 1-303-265-3024 Steve Mahoney, Production/Editorial Coordinator 1-781-734-8442: fax: 1-303-265-3198 Melissa Annand, Newsletter/Editorial Coordinator Contact for contributed technical articles 1-781-734-8443; fax: 1-303-265-3279 Adam Odoardi, Prepress Manager 1-781-734-8325; fax: 1-303-265-3042

#### CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

#### COLUMNISTS

Howard Johnson, PhD: Bonnie Baker; Joshua Israelsohn; Pallab Chatterjee

#### PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Kelly Jones, Production Manager 1-781-734-8328; fax: 1-303-265-3164 Linda Lepordo, Production Manager 1-781-734-8332; fax: 1-303-265-3015

#### EDN EUROPE

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

#### EDN ASIA

Raymond Wong, Managing Director/ Publishing Director raymond.wong@rbi-asia.com Kirtimaya Varma, Editor in Chief kirti.varma@rbi-asia.com

#### **EDN CHINA**

William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu, Executive Editor johnmu@idg-rbi.com.cn

#### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Takatsuna Mamoto, Editor in Chief t.mamoto@reedbusiness.ip

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community.

#### **DENNIS BROPHY**

Director of Business Development. Mentor Graphics

#### DANIS CARTER

Principal Engineer, Tyco Healthcare

#### CHARLES CLARK

Technical Fellow, Pratt & Whitney Rocketdyne

#### DMITRII LOUKIANOV

System Architect, Intel

#### RON MANCINI Retired Staff Scientist

GABRIEL PATULEA

#### Design Engineer, Cisco

DAVE ROBERTSON

#### Product Line Director, Analog Devices SCOTT SMYERS

VP Network and System Architecture Division, Sony

#### TOM SZOLYGA

Program Manager, Hewlett-Packard

JIM WILLIAMS Staff Scientist, Linear Technology

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000. Address changes or subscription inquiries: phone 1-800-446-6551; fax 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.getfreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345, Include your mailing label.

## Keep it Simple.

#### **NI CompactDAQ USB** Data Acquisition

- Now more than 30 modules

- New NI LabVIEW data-logging software included

- Hi-Speed USB for up to 6.4 MS/s streaming I/O

- Compact 25 by 9 by 9 cm form factor

>> For more information and pricing, visit ni.com/compactdaq/new

800 327 9894

© 2007 National Instruments Corporation. All rights reserved. LabVIEW, National Instruments, NI, ni.com, and NI CompactDAQ are trademarks of National Instruments. Other product and company names listed are trademarks or trade names of their respective companies. 2006-8345-301-101-D

## reate any kind of wavefo

With the industry's best-selling function generators.

Agilent 33220A Function Generator

|                                            | <b>33220A</b><br>20 MHz Sine & Square | <b>33250A</b><br>80 MHz Sine & Square |

|--------------------------------------------|---------------------------------------|---------------------------------------|

| Basic Waveforms                            | 11 Built-in Lov                       | v Distortion                          |

| Pulse                                      | Variable Edge 5 MHz                   | Variable Edge 50 MHz                  |

| Arbitrary Waveforms                        | 14-bits, 64K points                   | 12-bits, 64K points                   |

| <b>Modulation</b><br>(Internal / External) | AM, FM, PM, FSK & PWM                 | AM, FM & FSK                          |

| Open Connectivity                          | USB, GPIB & LAN                       | GPIB & RS232                          |

| Price (USD, Subject to ch                  | ange) \$1,853.00                      | \$4,553.00                            |

#### STANLEY

800-225-5370 Supply & Services www.stanleysupplyservices.com/FuncGen

u.s. 1-800-829-4444 canada 1-877-894-4414

www.agilent.com/find/functiongens2

For waveform generation, more people turn to Agilent than anyone else.

The Agilent 33220A and 33250A produce almost any kind of waveform you can imagine. You'll have built-in modulation, sweep, and burst capabilities. You'll be able to generate pulses and create arbitrary waveforms using up to 64K points of memory. With this much functionality, the possibilities are endless.

Agilent function generators come with free IntuiLink software and industry standard I/O connectivity for your PC. Built for both R&D and manufacturing use, the 33220A and 33250A add value to every stage of the design cycle.

To learn more, go to www.agilent.com/find/functiongens2

**USB-powered RF-power sensor combines** most measurement functions

gilent Technologies has announced the U2000 Series of USB-based 9-kHz to 24-GHz power sensors, which are smaller, lighter, and less expensive than typical power meters and similar power-sensing instrumentation. Because the new sensors operate without power meters or extra hardware modules, they save bench space and

**CC** With the rising need for multiplechannel power measurements in various industries, these power sensors are the affordable, simple solution that our customers have requested."

simplify RF-power measurements in crowded work areas. The sensors work with a variety of Agilent spectrum analyzers and network analyzers and thus extend those instruments' abilities to make accurate average-power measurements. In addition to fast and easy setup with plug-and-play USB con nectivity, the sensors, in combination with the N1918A Power Analysis Manager software, also simplify monitoring and troubleshooting. Because the USB-powered sensors provide built-in triggering, they require no external power adapters or triggering modules for synchronization with external instruments or events.

"The USB sensors' ability to operate without a power meter marks a breakthrough in our offerings for power measurements," says Ee Huei Sin, vice president and general manager of Agilent's Basic Instruments Division. "With the rising need for multiple-channel power measurements in various industries, these power sensors are the affordable, simple solution that our customers have requested."

According to Gooi Soon Chai, vice president and general manager of Agilent's Electronic Instruments Business Unit, the highly portable units demonstrate Agilent's commitment to providing affordable, reliable, and continually improved test-and-measurement products. The series includes four models that deliver as many as 250 readings/sec and a -60 to +20-dBm power range. Each sensor includes

The U2000 Series USB-powered RF-power sensors are small, fast, light, and-except for the results display, which you see on a host computer-complete. The single small module replaces a conventional sensor and a power meter. With a conventional sensor, the meter not only displays the measurement results, but also supplies power to the sensor and conditions the sensor's output.

a high-speed USB 2.0 interface for simple, quick setup. With internal zeroing capability, calibration does not require disconnecting the sensor from the device under test, hence reducing test time and sensor wear and tear.

With the N1918A Power Analysis Manager software, the sensors display powermeasurement results on a PC or another appropriate instrument. In addition to the normal waveform-monitoring option, the software eases monitoring and troubleshooting through functions such as limit and alert settings, record and playback, multiple-list view, overlay, and channel mathematics. Prices starts at \$2300.

-by Dan Strassberg ▶Agilent Technologies, www.agilent.com/find/ usbsensor\_pr.

#### **FEEDBACK LOOP**

"Surface-mount jacks make no sense. I've resoldered my share (and not because I'm careless). All it takes is a drop with the plug still in, and buh-bye to connection."

—Reader Dan Kingsbury speaks out, in *EDN*'s Feedback Loop, at www.edn.com/article/CA6447234. Add your comments.

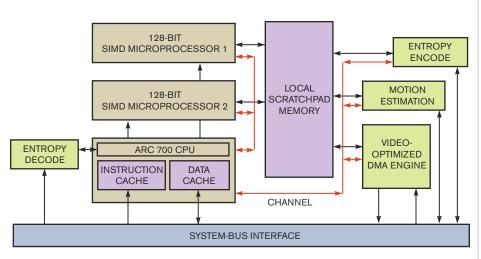

#### Video-codec cores offer programmability

s more and more devices-from cell phones to surveillance cameras to robots-require video capture, video codecs are becoming almost standard building blocks for SOCs (systems on chips). Given the complexity of the computing tasks involved, this area might appear to be one in which specialized hardware will reign unchallenged. But an Aug 13 introduction from ARC International disputes

ARC, a long-standing vendor of customizable RISC cores, has argued for years that properly augmenting a RISC core with SIMD (single-instruction/multiple-data) execution engines enables that

core to handle tasks well beyond the range of a CPU alone. The company supports this argument with a family of-for now-five video-codec subsystems, each comprising an ARC 700 RISC core, one or more SIMD units, and specialized hardware.

The advantage of putting the heavy-lifting burden onto programmable hardware is flexibility. These new ARC VRaptor cores come with supporting software for H.263, H.264, MPEG-4, JPEG, VC-1, and a variety of other codecs. They are adaptable to custom applications, such as the H.264/video-analytics blends that are starting to find use in video surveillance. The disadvantage of the programmable approach, traditionally, has been high power consumption for relatively low performance. And, although advanced processes and aggressive power management have to some degree mitigated this problem, physics issues remain. Accordingly, high-end performance for the cores in this family is H.264 Base Profile, D1-resolution encoding at 30 frames/sec.

You must use this benchmark with some care, however, because you can speed things up in a software-driven codec by disabling procedures that improve picture quality or reduce bit rate. Conversely, if you turn on all the bells and

whistles for excellent picture quality, you can slow down the encoder operation. And power increases with clock frequency and activity, so the more bells and whistles, the more milliwatts the system consumes. For this and other reasons, ARC quotes power-consumption figures only under a nondisclosure agreement.

The underlying hardware for the high-end core includes a 700-series RISC CPU core, local memory, a sophisticated DMA arrangement, two SIMD units, and special hardware blocks for motion encoding and for entropy encoding and decoding. The SIMD units are extensions of ARC's standard SIMD engine, with additional instructions for dealing with video-processing tasks. The specialized units are dedicated hardware blocks with some degree of programmability to accommodate differences in codec requirements. In operation, the RISC core handles sequencing and control, and the SIMD engines take on the high-bandwidth tasks, such as pixel-level transforms and deblocking.

ARC estimates that the highend 417V core will be slightly larger than 10 mm<sup>2</sup>, including all internal-RAM structures, in TSMC's (Taiwan Semiconductor Manufacturing Co, www. tsmc.com) 130g process, using Cadence's (www.cadence. com) layout flow and Virage Logic (www.viragelogic.com) libraries. Engineers have extensively simulated the cores and verified them in FPGA emulation, and they are available now. For more on these products, see "Video codecs in software: some reflections on programmable-hardware approaches," www.edn.com/070913p1.

-by Ron Wilson >ARC, www.arc.com.

VRaptor combines an ARC RISC core with both programmable and fixed-function units.

#### **DILBERT By Scott Adams**

## BUILT TO LAST

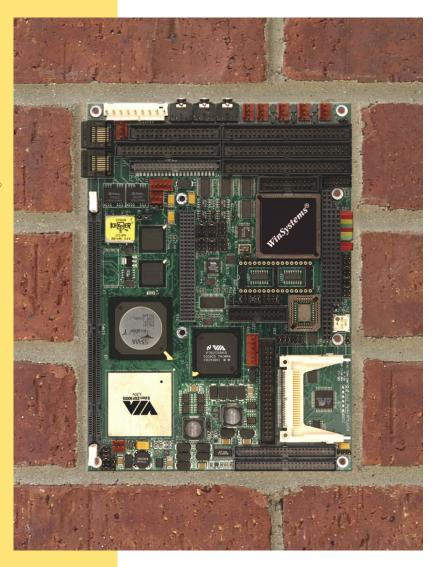

## Fanless EBX 733MHz P3 with COM, dual ENET, USB and Video

- VIA 733MHz or 1GHz C3 CPU

- PC-compatible, supports Windows<sup>®</sup>

XP, CE, Linux and x86 RTOS

- Up to 512MB PC133 SDRAM

- Up 1GB bootable DOC®, 512KB SRAM, or 1MB EPROM

- Type I and II CompactFlash cards supported up to 8GB

- CRT, flat panel, and LVDS

- Two 10/100 Ethernet controllers

- Four USB ports

- Four serial COM ports

- LPT, Kybd, and mouse

- 48 bi-directional I/O lines

- Two EIDE and one floppy disk controller

- AC97 Audio supported

- PC/104 & PC/104-Plus expansion

- +5 volt only operation

- EBX size: 5.75" x 8.0" (146 mm x 203 mm)

- -40° to +85°C operation (733MHz)

- Quick Start Developers Kits for Windows® XP, CE, and Linux

- Immediate availability

The EBC-C3 embeds 9 different functions to provide a processor- and I/O-intensive solution. It operates over a -40° to +85°C temperature range without the need of a fan, making it ideal for embedded applications such as robotics, MIL/COTS, transportation, pipeline, and machine control.

It runs Windows® CE, Windows® XP embedded, Linux, and other operating systems as VxWorks and QNX. And its x86-PC software compatibility assures a wide range of tools to aid in your application's program development and checkout.

Call 817-274-7553 or Visit www.winsystems.com

Ask about our 30-day product evaluation!

715 Stadium Drive • Arlington, Texas 76011 Phone 817-274-7553 • FAX 817-548-1358 E-mail: info@winsystems.com

#### Cadence and Mentor create free, open-source SystemVerilog methodology

n an effort to make it easier for users to create interoperable SystemVerilog verification flows, Cadence Design Systems and Mentor Graphics have jointly created and are announcing that they will standardize on the free, opensource OVM (Open Verification Methodology). Steve Glaser, corporate vice president of marketing in the verification division at Cadence, and Dennis Brophy, director of strategicbusiness development at Mentor, say that each EDA vendor offering SystemVerilog simulation flows has so far developed its own guidelines. Users must adopt these guidelines to develop verification IP (intellectual property) for their flows. Mentor has offered the AVM (Advanced Verification Methodology), and Mentor has offered the UVM (Unified Verification Methodology).

"Our customers have noticed that we've continued down this path of using our own proprietary, company-centric methodologies because they have to support N number of ways of doing things on  $N \times N$  number of tools, which is making their job of porting verification information a challenge," says Brophy. "What we have been doing is hampering design collaboration."

Today, for example, a user could develop a piece of VIP (verification IP), such as a SystemVerilog testbench or a transaction-level or RTL (register-transfer-level) model using one vendor's format, but that VIP might not easily work in the other vendor's SystemVerilog simulation environment. "Users would essentially have to do the work

themselves and build a bridge between the two vendors' environments to make the VIP work in the other's tool environment," says Brophy. "The new OVM will eliminate the need for users to create that bridge on their own. We are enabling a truly interoperable VIP environment, promoting language interoperability and enabling data portability across multiple simulator platforms to deliver on the promise of SystemVerilog and open up a healthy and vibrant designand-verification community."

The new methodology is a direct competitor and a competitive response to Synopsys' proprietary VMM **SystemVerilog** guidelines.

The new OVM is a superset of AVM and UVM, and Cadence and Mentor each dedicated developers to combine the best of both worlds to create OVM. The OVM deliverables include the OVM Methodology, which comprises how-to documentation, examples, and code snippets, and an OVM class library-essentially the building blocks to develop VIP.

Glaser and Brophy say that the OVM will allow customers and third-party providers of VIP to create testbenches and models in one format that will run in any OVM-compliant tool environment. "We tried to look at this problem quite ho-

listically and said that to enable this methodology, we had to standardize on an open set of functional building blocks, called class libraries. But there are a lot of methodological implications that then connect into even higher-level library functions and even into the way that tools need to interpret data and the way that customers need to take IP from different sources and configure it for different parameters. They then start operating it, controlling it, and being able to get messages back," says Glaser. "There are a lot of considerations for plug-and-play IP from multiple sources as well as the path from block to chip to systemlevel reuse, which tends to bring in other languages such as SystemC." Brophy and Glaser claim that OVM addresses all those issues and fully complies with the IEEE OpenVerilog language standard 1800-2005.

At least initially, the new methodology is a direct competitor and a competitive response to Synopsys' (www. synopsys.com) proprietary VMM SystemVerilog guidelines, which also comply with IEEE 1800-2005. Synopsys has been a proponent of SystemVerilog and, some would say, the front-runner in the market ever since a few years ago when it acquired Co-Ware Design Automation, the company that originally developed SystemVerilog. But the VMM, say Glaser and Brophy, has been less than open and has lacked significant links into SystemC. (Industry participants viewed SystemVerilog and SystemC as competing languages when they debuted a few years ago.)

However, both Brophy and Glaser claim that Synopsys has in the past declined to join any open SystemVerilog efforts. Synopsys and all other vendors are free to adopt the OVM at any point, and broad adoption of a single viable SystemVerilog methodology would help users use their multivendor SystemVerilog-tool flows and would likely increase the use and general sales of SystemVerilog tools and methods. "We think OVM will be a great step toward speeding up the adoption of SystemVerilog and advanced verification methodologies," says Glaser.

Both companies had to modify their SystemVerilog simulation environments so that they could run VIP created using the OVM guidelines. Both companies have verified that their simulation platforms, Mentor Questa and Cadence Incisive, can run VIP created with the OVM guidelines. Brophy notes that making the tools OVMcompliant wasn't a painstaking process, so it should be fairly easy for other vendors to make their tools OVM-compliant.

The companies are offering the free OVM as the Apache 2.0 open-source license. The companies will initially offer it to selected customers in the third quarter of this year and plan to make the production release, which includes the methodology and supporting library, in the fourth quarter of this year. Initially, Apache 2.0 will be available for downloading from Cadence's and Mentor's Web sites, but plans are in the works to eventually make it available from a dedicated Web site.

-by Michael Santarini Cadence Design Systems, www.cadence.com.

**▶Mentor Graphics**, www. mentor.com.

## Connect...

to PCI Express, Gigabit Ethernet & Serial RapidIO

#### **Low-Cost FPGAs with Transceivers**

Connect now with Arria™ GX FPGAs, the only risk-free, low-cost FPGAs with transceivers.

With protocol-optimized support for PCI Express, Gigabit Ethernet, and Serial RapidIO<sup>™</sup> applications, Arria GX FPGAs offer superior signal integrity, proven transceiver technology, robust flip-chip packaging, and award-winning design tools.

Make the right connections with Arria GX FPGAs. And turn your unique ideas into products—swiftly, smoothly, and cost-effectively.

The Programmable Solutions Company®

www.altera.com/arriagx

#### Processor lowers the cost and power thresholds for HD video

he TMS320DM355 processor is the latest addition to Texas Instruments' DaVinci processor family. Unlike previous Da-Vinci devices, this processor does not include a softwareprogrammable DSP. Rather, it couples an ARM936EJ-S core with a video-processing subsystem and MPEG-4 JPEG coprocessor that are configurable through software executing on the ARM core. The less-than-\$10 processor enables HD (high-definition)video products, such as digital cameras and IP (Internet Protocol) videocameras targeting a \$250 end-unit price, as well as digital-photo frames and video baby monitors targeting a \$120 end-unit price. Going with a configurable hard coprocessor instead of a software-programmable DSP helps the system deliver power consumption as low as 400 mW to support HD MPEG-4

encoding and approximately 1 mW in standby; this power-consumption level allows for 80 minutes of continuous HD-video capture with two AA batteries.

The processor supports HD MPEG-4 SP encoding or decoding at 720p and 30 frames/ sec and JPEG encoding or decoding at 50M pixels/sec. It is available in 216- or 270-MHz clock speeds; these devices support only these rates because the video subsystem and coprocessor blocks operate at the same clock rate as the processor. The video-processing subsystem is the same set of engines that all DaVinci devices feature. The processor supports the same intellectualproperty and API (applicationprogramming-interface) model as the other DaVinci devices. It includes production-qualified, configurable HD MPEG-4 and JPEG codecs without licensing fees or royalties. The

peripheral suite includes a high-speed USB 2.0 OTG (On-The-Go) device and mini-host with a PHY (physical) layer, a 10-bit DAC, 32 kbytes of program/data memory, 8 kbytes of ROM, 16- and 8-kbyte instruction and data caches, and an external memory interface that supports mobile DDR/ DDR2.

The DM355 is available for sampling now in a 13×13-mm, 329-pin, 0.65-mm-pitch BGA package. The 216-MHz device sells for \$9.75 (50,000), and the 270-MHz device sells for \$11,49 (50,000). The TMDX-EVM355 evaluation module is available now for \$495. It includes JPEG/MPEG-4 SP/ G.711 codecs, ORCAD schematics, and MontaVista Linux with drivers for the peripherals, video-processing subsystems, and Uboot loader.

-by Robert Cravotta >Texas Instruments, www.

#### Module controls four network channels

new 3U CompactPCI network controller from MEN Micro offers four fast Ethernet ports for control of multiple network

The F211 network controller features quad fast Ethernet channels for flexible control of multiple network configurations.

configurations, including firewalls, gateways, routers, and fieldbus-data concentrators. The single-slot F211 controller features four full- or half-duplex channels that support 10BaseT and 100BaseTX physical layers and provide autonegotiation, collision, and link detection with a maximum data transfer of 200 Mbps. Each of the four channels has a unique MAC/IP (media-accesscontrol/Internet Protocol) address, enabling the F211 to function in a redundant mode when you use the lines in parallel for high-availability systems. For harsh and mobile applications, the 32bit, 33-MHz F211 operates over an extended temperature range of -40 to +85°C. The controller comes with software drivers for the Windows, Linux, QNX, and VxWorks operating systems. Price for the F211 is \$544, and delivery is within six weeks.-by Warren Webb

▶ MEN Micro Inc, www.men.de.

#### REFERENCE **DESIGN** PREVENTS **POWER THEFT**

Some people respond to the high cost of energy by stealing it. To prove that fact, Metering.com recently published a report showing that, in some countries, tampering with meters accounts for 5% of illegally consumed electricity. That tampering doesn't happen just in Third World countries, either: The report estimates that losses in the United States are approximately 4%. According to Silvestro Fimiani, productmarketing manager for the company, the most common way to disable meters is to use a large permanent magnet to provide an intense external magnetic field.

Energy thieves can saturate former core with a large per-

Addressing this problem, Power Integrations has published a reference design based on its LinkSwitch XT family. The design, for an isolated power supply in flyback configuration, delivers 150 mA at 5V, and an external magnetic field does not affect it. It also consumes just 1W and produces the regulated 750 mW that advanced meter electronics require.-by Margery Conner Power Integrations, www.powerint.com.

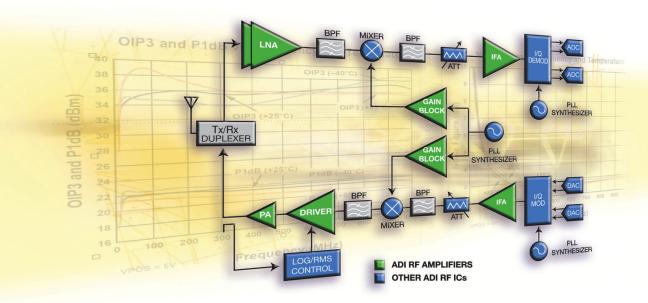

## The highest performance RF amplifiers. Across the signal chain, analog is everywhere.

#### Low Noise Amplifiers (LNA)

| Part<br>Number | Freq Range<br>(MHz) |      |      | P1dB<br>(dBm) |     |    | Specs @<br>(MHz) | Price  |

|----------------|---------------------|------|------|---------------|-----|----|------------------|--------|

| ADL5521        | 400 to 4000         | 15.3 | 35.3 | 22.5          | 0.8 | 65 | 1950             | \$2.15 |

| ADL5523        | 400 to 4000         | 17.5 | 33.7 | 21.9          | 1.0 | 65 | 1950             | \$2.15 |

#### **Intermediate Frequency Amplifiers (IFA)**

| Part<br>Number    | Freq Range<br>(MHz) | Gain<br>(dB) | OIP3<br>(dBm) | P1dB<br>(dBm) | NF<br>(dB) | Current<br>(mA) | Specs @<br>(MHz) | Price  |

|-------------------|---------------------|--------------|---------------|---------------|------------|-----------------|------------------|--------|

| ADL5530*          | DC to 1000          | 16.8         | 37.0          | 21.8          | 3.0        | 110             | 190              | \$1.56 |

| ADL5531           | 20 to 500           | 20.3         | 40.9          | 20.7          | 2.7        | 101             | 190              | \$2.25 |

| ADL5532           | 20 to 500           | 16.1         | 39.1          | 19.7          | 3.0        | 95              | 70               | \$2.25 |

| ADL5533<br>(75 Ω) | 30 to 1000          | 19.8         | 37.3          | 18.7          | 2.9        | 66              | 70               | \$2.55 |

| ADL5534<br>(Dual) | 20 to 500           | 19.8         | 41.8          | 20.0          | 2.5        | 90              | 70               | \$3.29 |

#### **Gain Blocks**

| Part<br>Number | Freq Range<br>(MHz) | Gain<br>(dB) | OIP3<br>(dBm) | P1dB<br>(dBm) | NF<br>(dB) | Current<br>(mA) | Specs @<br>(MHz) | Price  |

|----------------|---------------------|--------------|---------------|---------------|------------|-----------------|------------------|--------|

| AD8353*        | 1 to 2700           | 19.5         | 22.8          | 8.3           | 5.6        | 42              | 900              | \$0.48 |

| AD8354*        | 1 to 2700           | 19.5         | 19.3          | 4.8           | 4.4        | 25              | 900              | \$0.48 |

| ADL5541        | 50 to 6000          | 14.7         | 39.2          | 16.3          | 3.8        | 92              | 2000             | \$1.65 |

| ADL5542        | 50 to 6000          | 18.7         | 39.0          | 18.0          | 3.2        | 92              | 2000             | \$1.65 |

#### **Driver Amplifiers**

|                | •                   |              |               |               |     |                 |                  |        |

|----------------|---------------------|--------------|---------------|---------------|-----|-----------------|------------------|--------|

| Part<br>Number | Freq Range<br>(MHz) | Gain<br>(dB) | OIP3<br>(dBm) | P1dB<br>(dBm) |     | Current<br>(mA) | Specs @<br>(MHz) | Price  |

| ADL5320        | 400 to 2700         | 13.7         | 42.0          | 25.6          | 4.2 | 104             | 2140             | \$2.55 |

| ADL5322        | 700 to 1000         | 19.9         | 45.3          | 27.9          | 5.0 | 320             | 900              | \$3.48 |

| ADL5323        | 1700 to 2400        | 19.5         | 43.5          | 28.0          | 5.0 | 320             | 2140             | \$3.48 |

<sup>\*3</sup> V bias is also supported

All prices shown are \$U.S. in 1k quantities unless otherwise noted

## LNAs, IFAs, Gain Blocks, Drivers: Fully Specified for Performance-Driven Applications

Introducing four new RF amplifier families engineered for telecommunications infrastructure and other demanding wireless applications. Each family member is fully specified over frequency, temperature, and supply voltage to minimize the need for extensive device characterization.

All of our new RF amplifiers offer unique performance advantages, such as higher linearity, lower noise, and lower supply current. Many also offer additional features, such as internal active bias, internal matching, ESD protection, and some dual configurations. Analog Devices offers high performance RF ICs across the entire signal chain, simplifying the development and supply chain process while accelerating time-to-market.

Analog Devices' RF amplifier portfolio provides best-in-class performance, integration, and price. For more information about these new RF amps, as well as ADI's other solutions for RF designs, call 1-800-AnalogD or visit www.analog.com/rfamps-ad.

RF amplifiers available in 8-lead LFCSP, 16-lead LFCSP, and SOT-89 packages—from 6 mm² to 16 mm²—with single/dual options

#### **MRESEARCH UPDATE**

BY RON WILSON

## Los Alamos lab makes major step in quantum-dot lasers

ictor I Klimov, PhD, leads a team at Los Alamos National Laboratory that has been working for a number of years on turning NQDs (nanocrystal quantum dots) into lasers. Because the dots are so small, their size influences the energy gap between the conduction and the valence bands. When the recombination of an electron-hole pair causes the release of light in a laser, the color of the light relates to the energy gap. Hence, Klimov and company could change the color of an NQD laser simply by fabricating larger or smaller dots-if they could get the NQDs to be lasers.

However, for reasons that again relate to the size of the dots, you must have more excited electrons than valence-band electrons in a dot to get light amplification. An incoming photon hits one excited electron, an action causing the emission of a photon. However, if you don't excite most of the

valence electrons, odds are that the next unexcited electron will just absorb the emitted photon. You might think the solution is just to excite more of the electrons, but there is a problem with this approach, too.

Again because of quantum effects, electron-hole pairs and neighboring electrons interact to recombine quickly in NQDstoo quickly to permit laser action and without releasing a photon. Recently, however, Klimov and his team have reported that, by fabricating nanocrystals with a cadmium-sulfide core surrounded by a zinc-selenide shell, the physical interface separates the conduction-band electrons from the corresponding holes in the valence band, substantially slowing recombination and making light amplification possible. A conceivable result could be nanosized, color-to-order lasers for sensing and optical interconnect.

► Los Alamos National Laboratory, www.lanl.gov.

## Silicon nanocrystals promise 40% solar-cell efficiency

A research team at the NREL (National Renewable Energy Laboratory) claims to have observed production of two to three electrons from a single photon in a silicon nanocrystal. The result is potentially highly significant for the photocell business. Scientists had previously thought that silicon could produce only one excited electron per photon—limiting the conversion efficiency of silicon photocells without the aid of light-concentrating hardware to approximately 20 to 30%.

Previously, other researchers had observed multiple-electron production in exotic materials, but these substances offered little hope of production in the volumes necessary to impact the world's growing energy needs. The NREL work, in contrast, used ordinary silicon. The trick is that these researchers confined the silicon into nanocrystals. The fact that the

A 7-nm chunk of crystalline silicon could dramatically increase the efficiency of solar cells. size of the crystal approaches atomic scale means that the behavior of subatomic particles, such as electrons, in the material can fundamentally differ from their behavior in the same material in bulk.

Some questions about the methodology remain, because researchers can only indirectly observe electron production in photovoltaics of this type. And no one has contemplated mass production of large arrays of quantum dots. But nanocrystals of semiconductor ma-

terial are relatively easy to produce through solution chemistry, so such problems may not turn out to be showstoppers. The payoff could be commercial photovoltaic panels with as much as 40% unaided efficiency.

**⊳National Renewable Energy Laboratory**, www.nrel.gov.

#### NANOSTRUCTURES ENABLE PAPERLIKE SUPERCAPACITORS AND BATTERIES

The carbon nanotube has made another appearance in the literature, this time giving researchers quite a charge. Researchers at Rensselaer Polytechnic Institute have reported the use of the structures in creating a family of thin, paperlike batteries and supercapacitors.

The researchers observe that batteries, capacitors, and devices that combine those functions in application-specific ways all rely on the same three elements: an electrode material, a dielectric material, and a nonreactive matrix to support the other two. Starting from this conceptual basis, the researchers created a thin matrix of cellulose fibers-essentially, a very clean sheet of paper. They then developed a technique for diffusing carbon nanotubes into the paper in a way that leaves the tubes aligned with each other. The resulting structure acts as a very-low-effective-resistance elec-

trode with an enormous effective surface area. By then diffusing a nonaqueous electrolyte into the sheet of paper, the sheet can become a battery, a capacitor, or a combination of the two, depending on the choice of electrolytes and the patterns in which you diffuse them.

The whole structure retains its paperlike characteristics. You can twist, roll, fold, or stack it to make multicell batteries or capacitors, and you can trim it to shape, all without destroying its electrical properties. In addition, because all three materials behave well over temperature, batteries using the structures can operate over a very wide temperature range. The researchers' paper appeared in the Aug 15, 2007, Early Edition of the Proceedings of the National Academy of Sciences (www.pnas.org).

Rensselaer Polytechnic Institute, www.rpi.edu.

## More 16-bit DAC performance for more designs. In process control, analog is everywhere.

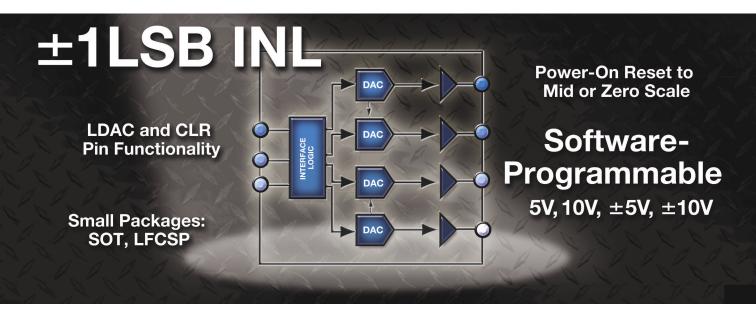

#### AD5064

#### **High Performance for Open-Loop Systems**

The first low voltage quad with  $\pm 1$  LSB INL @ 16 bits. Unmatched accuracy and pin functionality, combined.

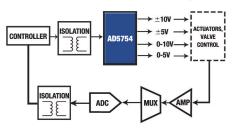

#### AD5754 Flexible Solution for Closed-Loop Systems

The AD5754 provides a software selectable output range of 5 V, 10 V,  $\pm 5 \text{ V}$ , and  $\pm 10 \text{ V}$  for cost-efficient system configuration.

#### New Levels of Performance and Flexibility for Open-Loop and Closed-Loop Applications

Our newest portfolio of industrial 16-bit DACs offers best-in-class performance, and a world of system configuration possibilities. You'll find single, dual, and quad option DACs, in small packages, with a full range of design tools and support. In addition to these DACs, Analog Devices offers hundreds of other IC solutions to meet all your process control needs. For more information, visit <a href="https://www.analog.com/16-bitDACs">www.analog.com/16-bitDACs</a> or call 1-800-AnalogD.

| Part No.            | Description                                                                                   | Price   |  |  |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------|---------|--|--|--|--|--|--|

| Ideally Suited to O | Ideally Suited to Open-Loop                                                                   |         |  |  |  |  |  |  |

| AD5060              | Single, 5 V, $\pm 1$ LSB INL (max), 1 mA @ 5 V                                                | \$7.50  |  |  |  |  |  |  |

| AD5065              | Dual, 5 V, ±1 LSB INL (max), 2.3 mA @ 5 V                                                     | \$11.25 |  |  |  |  |  |  |

| AD5064              | Quad, 5 V, $\pm 1$ LSB INL (max), 5 mA @ 5 V                                                  | \$15.95 |  |  |  |  |  |  |

| AD5764              | Quad, ±15 V, ±1 LSB INL (max)                                                                 | \$35.70 |  |  |  |  |  |  |

| Ideally Suited to C | llosed-Loop                                                                                   |         |  |  |  |  |  |  |

| AD5752              | Dual, software-programmable output range of 5 V, 10 V,<br>±5 V, ±10 V in 24-lead TSSOP        | \$6.95  |  |  |  |  |  |  |

| AD5754              | Quad, software-programmable output range of 5 V, 10 V, $\pm$ 5 V, $\pm$ 10 V in 24-lead TSSOP | \$10.05 |  |  |  |  |  |  |

| AD5664R             | Quad, 5 V, 5 ppm ref, in 3 mm $	imes$ 3 mm LFCSP                                              | \$10.45 |  |  |  |  |  |  |

All prices shown are \$U.S. at 1k quantities unless otherwise noted. All parts 16-bit resolution.

#### BY GARY GIUST, PHD

#### Jitter peaking and PLLs

y audiophile brother prizes his tube transistors and vinylrecord collection. It doesn't bother him that every pass of the metal needle on vinyl creates friction that slowly degrades his records' fidelity. Engineers creating clock trees by cascading several PLL (phase-locked-loop) chips may relate to this situation. Jitter peaking with each PLL acts as a "needle" that degrades the timing of the input signal, or "record."

INDIVIDUAL PLL

JITTER-TRANSFER PLOTS

JITTER-TRANSFER PLOT

GAIN (dB)

(a)

BANDWIDTH

MODULATION (JITTER) FREQUENCY

(b)

PLL 3

(d)

PLL 2

PLL 3

PLL 2

PLL 3

(e)

PLL 2

PLL 3

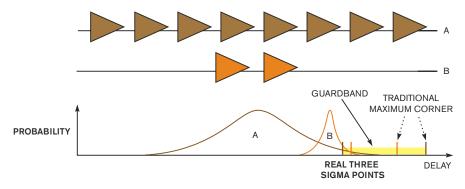

Figure 1 Cascading three identical PLLs amplifies jitter peaking (a). Avoid this problem by selecting overdamped PLLs (b), three different PLLs (c), the lowest bandwidth for the last PLL (d), or an alternative clock tree (e).

As this signal passes through subsequent PLLs, jitter peaking can accumulate to cause instability or timing failures. Figure 1a shows a worst-case scenario in which a chosen PLL with significant peaking connects three times in series, causing this peaking to accumulate. The first question to ask in this situation may be surprising: Is jitter peaking really a problem?

Just because jitter peaking exists doesn't mean there is a problem. First, consider the application. Most PLLs exhibit some degree of peaking—typically, 3 dB and not all applications require the tightest timing margins. At the other extreme, architectures based on cascaded regenerators cannot permit jitter peaking to accumulate unbounded. For example, SONET (synchronous-optical network) specifies less-than-0.1-dB peaking. Another way to analyze this issue is to ask: What signals and noise are present in the system? If there is no frequency content in which jitter peaking occurs, then this peaking has little impact on system performance, assuming that the PLL is stable. In other words, if the needle wears a groove in the "vinyl" that you cannot hear or, in my brother's

case, feel, then there is little impact.

What if jitter peaking is a problem? One approach cascades only PLLs having overdamped loops common in applications such as SONET (Figure 1b). However, this approach increases cost and limits chips selection. Figure 1c shows an approach that avoids using identical PLLs more than once in any clock-tree path. Because each PLL has a different bandwidth, the frequencies at which peaking occurs are staggered, making it difficult for peaking to compound. If multiple vendors act as second sources for the same chip, use each vendor's chip once rather than the same vendor's chip many times, because each company uses different process technologies and design approaches, causing the peaking to occur at different frequencies. When using spread-spectrum clocking to reduce EMI (electromagnetic interference), make sure each PLL's bandwidth is wide enough to pass the spread modulation.

Another approach doesn't restrict how you cascade PLLs, except that the last PLL has the lowest bandwidth of all devices in its path. Figure 1d shows that jitter attenuator PLL 3 filters any peaking that accumulates in the tree. However, because PLL 3 is averaging—not tracking—the inputphase error from this peaking, make sure that the PLL can tolerate any worst-case expected phase errors so that it remains locked at all times.

The simplest approach avoids cascading PLLs altogether, in which jitter peaking in any path depends on only one device (Figure 1e). When this approach is impossible, request jitter peaking data in decibels and hertz from potential vendors to help understand the impact of cascading their devices and in choosing your available options.EDN

Gary Giust, PhD, is a marketing manager at PhaseLink Corp. He also conducts seminars on jitter. Contact him at gary@jittertime.com.

# It's how you deliver the Dolby® high-definition audio experience.

What happens when Freescale meets Dolby®? You get a family of audio DSPs specifically engineered to deliver Dolby Digital Plus and Dolby TrueHD: the world's two leading technologies for high definition, multi-channel surround sound for next-generation DVD. Whether you're designing products for the home or broadcast equipment, Freescale audio DSPs assure you of a standing ovation. Just one more way Freescale is partnering with the world's smartest companies to make the world a smarter place. freescale.com/smarter

# **Technology ahead of everyone - Samsung**

Samsung Electro-Mechanics manufactures the world's fastest, brightest and thinnest products through high tech development. Imagine your world and Samsung will make it real.

Samsung Electro-Mechanics will be your most reliable partner.

▼ LED/LED BLU : Specialized High Power LED (1,3W Cool/Warm White) and Middle Power LED (RGB, R/G/B, Cool/Warm White) for signage, electric sign, scene and mood lighting

► Martin Cho (martinch@samsung.com)

▼ Camera Modules: Excellent image quality with high-resolution CMOS technology and advanced opto-mechanics, like autofocus (Piezo and VCA), 5MP 3X Zoom and DIS

► Yoon-Chul, Park (y.c.park@samsung.com)

₩ HDI/FCBGAs: High density interconnected PCB for mobile phone and FC BGA for CPU, chipset and memory, combining circuit miniaturization and build-up technology

► Man-Hun, Hur (martin.hur@samsung.com)

✓ Chip Components: Leading edge chip components including world-first ultra small MLCC based on nano materials and creative design simulation ►Sang-Koo, Kang (semksk@samsung.com)

▼ Precision Motors: Precision-geared solution and vibration motors based on integrated mechanical technology and hall technologies ▶ Brian Yoo (byoo@samsung.com)

☑ **Digital Tuners**: Total solution for multimedia device, including TV, set-top box and portable device; multiple functions coupled in single package or very small form factor possible

▶Young Lee (young20@samsung.com)

▼ Antennas: CBA (Ceramic Block Antenna at 6\*2\*1.5t) simplifies mobile tuning with easy connectivity. IMA (In Mold Antenna) provides enhanced features like space, cost, and performance using IML technology

**Network Modules**: Wireless connectivity solution; Bluetooth, wireless LAN, GPS, Wimax, ZigBee, UWB, NFC, and various combo solutions for current and LTE.

► Hyun-Seok, Jeong (jamejung@samsung.com)

Power Supplies: High efficiency, high power density, and high quality in Flat Panel Display (LCD-TV, PDP-TV) IT, computer and renewable energy devices

►Su-Jung, Jung (sj282.jung@samsung.com)

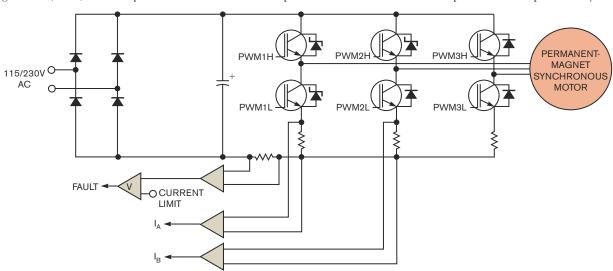

SENSORLESS VERSIONS OF THESE HIGHLY EFFICIENT MOTORS REDUCE COST AND PARTS COUNT, BUT THE MOTORS STILL REQUIRE COMPLEX CONTROL ALGORITHMS. MATCH THE RIGHT MOTOR TYPE AND CONTROL-LER TO YOUR APPLICATION FOR THE BEST PERFORMANCE AND COST.

PERMANENT-MAGNET MOTORS boost efficiency and power density

BY MARGERY CONNER • TECHNICAL EDITOR

he global price of energy is at an all-time high, with few signs of relief in sight, making consumers and businesses alike interested in energy conservation. Currently, the most common motor type in use is the single-phase ACIM (ac-induction motor), which is efficient only while running at a constant speed, though most applications—whether in the home or in industry—run at variable speeds. Worse, applications with a reverse speed, such as washing machines, require gearboxes, which reduce power density as well as efficiency. For high-power applications, using ACIMs is still the rule, but, at 2 kW and less, permanent-magnet motors are taking over in new designs. (As a reference, a washing-machine motor uses about 1 kW or less.)

Permanent-magnet motors have been commercially available since the '90s but didn't initially see widespread use because of the high cost that they owe to the expensive permanent magnets on their rotor. In addition, their complex control algorithms require specialized engineering expertise as well as the additional expense of an embedded processor (see sidebar "How permanent-magnet motors work" at the Web version of this article at www.edn.com/070913df).

Recently, however, the price of copper, which both the stator and the rotor windings of ACIMs use, has risen. These prices have had less impact on permanent-magnet motors, which lack rotor windings. At the same time, permanent-magnet prices have dropped.

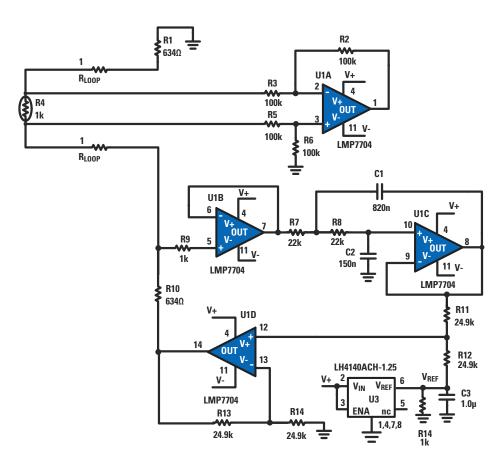

At their most basic, permanent-magnet motors require some kind of sensor—usually, a Hall-effect type—to determine the position of the rotor with respect to the windings on the stator. The motor's control-drive electronics use the rotor-position feedback to adjust the pulse-width-modulated drive signals to the windings. However, using sensors is not the only way for the control electronics to monitor position: Motorcontrol processors have become more powerful and can now calculate rotor position from the motor's back EMF (electromotive force), eliminating the need for position sensors for some applications (Figure 1). For example, new designs for hermetically sealed refrigeration compressors are moving to perma-

nent-magnet motors for higher power efficiency. Formerly, they relied on single-phase ACIMs, which required just two electrical connections through the hermetic seal. It's not a big leap for the designs to bring out one more line for a three-phase permanent-magnet motor drive, but bringing out three additional position-sensor lines through the hermetic seal would be too expensive and decrease reliability. Sensorless permanent-magnet motors are better options.

However, sensorless permanent-magnet motors are not the answers for all applications. The rotor must be moving at some minimum speed to generate a back EMF, which sensing requires. These devices are good only for motors in applications whose operating speed ranges from 5 to 100% of the top speed. In addition, applications requiring precise positioning usually require sensored motors. But, for applications such as consumer appliances and many industrial-control systems, sensorless permanent-magnet motors are making significant inroads.

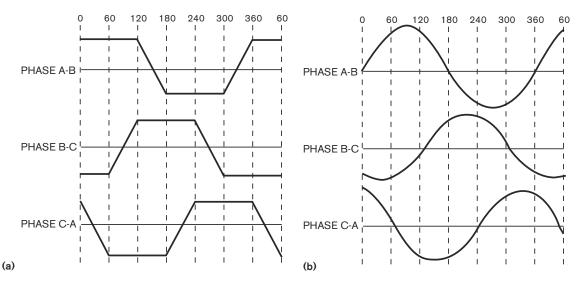

There are two kinds of permanent-magnet motors: brushless-dc motors and PMSMs (permanent-magnet synchronous motors). Brushless-dc-motor windings give a trapezoidal back EMF and respond to a trapezoidal-drive signal (Figure 2a); PMSMs produce a sinusoidal back EMF and require a sinusoidal-drive signal (Figure 2b). Their different drive signals and, thus, their torque make for

#### AT A GLANCE

- Permanent-magnet motors are more efficient than ac-induction motors, but they require more sophisticated control circuitry.

- Sensorless permanent-magnet motors are less expensive and more reliable than those with sensors, but some applications that require less-than-5%-of-maximum speed or frequent stops and starts require sensors.

- Microcontroller, DSC (digital-signal-controller), and semiconductor vendors are offering development platforms with control algorithms to ease the task of designing for these motors

a key difference in the drive characteristics of the two motors: The brushless-dc motor is subject to torque ripple of approximately 13%, and the PMSM theoretically has 0% torque ripple.

A six-step commutation process drives brushless-dc motors. As the process applies the drive voltage between two phases of the windings, the third phase senses the back EMF. The sequence to drive the rotor takes six steps; hence, manufacturers often call this sequence a six-step process. This algorithm is relatively straightforward, and you can implement it with an 8-bit processor or with an 8-bit processor and a hardware-

based coprocessor. Freescale, Infineon, Microchip, STMicroelectronics, and Texas Instruments have developed the software for the six-step commutation algorithms for their microcontrollers and DSCs (digital-signal controllers), which are, in general, 8-bit devices.

#### **FOC HELPS PMSMs**